Temperature Compensated Crystal Oscillator (TCXO) 7.0 x 5.0mm - CMOS

MV-TC645-7050T is a Temperature Compensated Crystal Oscillator (TCXO). This TCXO is analog temperature compensated, CMOS output device and comes in a FR4 base 7.0x5.0mm package. This device contains an internal voltage regulator resulting in excellent power supply rejection ratio.

The device is qualified to meet the JEDEC standard for Pb-Free assembly and compliant to the RoHS directive.

### **Electrical Performance**

| Parameter                           | Min       | Тур                | Max       | Units    |

|-------------------------------------|-----------|--------------------|-----------|----------|

| General                             |           |                    |           |          |

| Output Frequency                    | 10        |                    | 40        | MHz      |

| Operating Temperature               |           | -10/+70 to -40/+85 |           | °C       |

| Frequency Stability                 |           |                    |           |          |

| Stability Over Temperature          |           | ±5.0 to ±0.5       |           | ppm      |

| Initial Accuracy (25°C ±2°C)        |           |                    | ±2.0      | ppm      |

| Power Supply Stability (±5% Change) |           |                    | ±0.3      | ppm      |

| Load Stability (±10% Change)        |           |                    | ±0.2      | ppm      |

| Aging (1st year)                    |           |                    | ±1.0      | ppm/year |

| Start Up Time                       |           |                    | 2         | ms       |

| Package Size                        |           | 7.0 x 5.0 x 2.0    |           | mm       |

| upply                               |           |                    |           |          |

| Supply Voltage (Vdd)                |           | +3.3               |           | V        |

| Supply Current                      |           |                    | 10        | mA       |

| uning                               |           |                    |           |          |

| Tuning (Pull) Range                 |           | ±5 to ±10          |           | ppm      |

| Tuning Slope                        |           | Positive           |           |          |

| Control Voltage to reach Pull Range | 0.5       |                    | 2.5       | V        |

| Control Voltage Impedance           | 100       |                    |           | ΚΩ       |

| Output                              |           |                    |           |          |

| Output Signal                       |           | CMOS               |           |          |

| Output Logic Level                  |           |                    |           |          |

| Output Level - Logic High           | Vdd x 0.9 |                    |           | V        |

| Output Level - Logic Low            |           |                    | Vdd x 0.1 | V        |

| Output Load                         |           | 15 pF              |           |          |

| Output Rise and Fall Time           |           |                    | 3         | ns       |

| Duty Cycle                          | 45        |                    | 55        | %        |

| hase Noise & Jitter                 |           |                    |           |          |

| Phase Noise: (12.8 MHz)             |           |                    |           |          |

| 10 Hz offset                        |           | -93                |           | dBc/Hz   |

| 100 Hz offset                       |           | -123               |           | dBc/Hz   |

| 1kHz offset                         |           | -147               |           | dBc/Hz   |

| 10kHz offset                        |           | -155               |           | dBc/Hz   |

| 100kHz offset                       |           | -158               |           | dBc/Hz   |

#### Notes:

- 1 Initial Accuracy (25°C ±2°C) for "No Tuning" option is ±1.0ppm

- 2 Rise and Fall times measured from 20% to 80% of a full output swing

- 3 Power Supply pin should be filtered. e.g.  $0.1\mu F$  or  $0.01\,\mu F$  Capacitor for optimal performance.

- 4 Output is DC coupled

### **Maximum Ratings**

| (               |               |  |

|-----------------|---------------|--|

| Storage Temp    | -45°C to 95°C |  |

| Supply Voltage  | 0V to +7.0V   |  |

| Control Voltage | 0V to Vdd     |  |

| End May Ratings |               |  |

## **Maximum Ratings Notes:**

- ${\bf 1}\quad {\bf Stresses}\ {\bf in}\ {\bf excess}\ {\bf of}\ {\bf the}\ {\bf absolute}\ {\bf maximum}\ {\bf ratings}\ {\bf can}\ {\bf permanently}\ {\bf damage}\ {\bf the}\ {\bf device}.$

- 2 Exposure to absolute maximum ratings for extended periods may adversely affect device reliability.

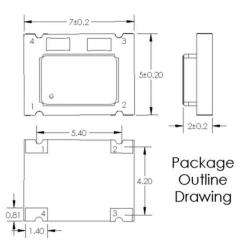

## **Package Information**

| Pin#    | Function                   |

|---------|----------------------------|

| Pin 1   | Vc = Control Voltage or NC |

| Pin 2   | GND = Ground               |

| Pin 3   | OUT = Output               |

| Pin 4   | Vdd = Supply Voltage       |

| End Pin |                            |

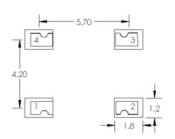

# Pad Layout

## **Handling and Construction**

| Package Construction       | FR4 base |   |

|----------------------------|----------|---|

| Moisture Sensitivity Level | MSL 1    |   |

| ESD, Human Body Model      | 500V     |   |

| ESD, Charge Device Model   | 500V     |   |

| End Handling               |          | 1 |

www.mv-electronics.com | +1 (717) 691-1582 | info@mv-electronics.com

**Ordering Information**

MV-TC645-7050T -

TCXO, CMOS -7.0 x 5.0 x 2.0mm, 4 Pins -  $B \times X \times - xxMxxxxx$

1 2 3 4

L Frequency

1 Voltage B: 3.3 V

2 Temp Range J: -10/+70 °C

H: -20/+70 °C K: -40/+85 °C

3 Temp Stability L: ±5.0 ppm M: ±2.5 ppm

N: ±2.0 ppm P: ±1.5 ppm

Q: ±1.0 ppm R: ±0.5 ppm

4 Tuning Range

X: No Tuning L: ±5 ppm K: ±8 ppm J: ±10 ppm